ADV7180зҡ„PCBеёғзәҝиҖғиҷ‘

ADV7180жҳҜй«ҳзІҫеәҰгҖҒй«ҳйҖҹгҖҒж··еҗҲдҝЎеҸ·еҷЁд»¶пјҢдёәиҺ·еҫ—жңҖдҪіжҖ§иғҪпјҢеҗҲзҗҶзҡ„PCBеёғзәҝжҳҜйқһеёёйҮҚиҰҒзҡ„гҖӮ

жЁЎжӢҹжҺҘеҸЈиҫ“е…Ҙ

жЁЎжӢҹиҫ“е…Ҙзәҝеә”иҜҘе°ҪеҸҜиғҪзҹӯпјҢ并е°ҪеҸҜиғҪдҝқжҢҒ75欧е§Ҷзҡ„йҳ»жҠ—гҖӮ

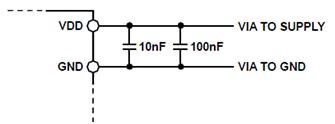

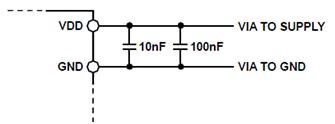

з”өжәҗеҺ»и—•

з”өжәҗзҡ„еҺ»и—•пјҢжҺЁиҚҗдҪҝз”ЁдёҖдёӘ0.1uFе’Ң10uFзҡ„з”өе®№пјҢеҺ»и—•зӮ№зҮғи·қзҰ»з”өжәҗз®Ўи„ҡдёҚиҰҒи¶…иҝҮ0.5CMпјҢеә”иҜҘдёҺиҠҜзүҮеӨ„дәҺеҗҢдёҖйқўдёҠпјҢд»ҘйҒҝе…ҚиҝҮеӯ”зҡ„еӯҳеңЁпјҢеҸҰеӨ–пјҢз”өжәҗеә”иҜҘе…Ҳз»ҸиҝҮеҺ»и—•з”өе®№пјҢ然еҗҺжүҚеҲ°з®Ўи„ҡпјҢиҝҷдёӘйЎәеәҸдёҚиғҪжҗһй”ҷпјҢиҝҷж ·з”өжәҗз”өжөҒжүҚиғҪе…Ҳз»ҸиҝҮз”өе®№пјҢ然еҗҺеҲ°иҠҜзүҮпјҢжүҚдјҡиө·еҲ°ж»Өжіўж•ҲжһңпјҢеҗҰеҲҷе°ұдјҡеӨ§еӨ§йҷҚдҪҺеҺ»и—•зҡ„ж•ҲжһңпјҢеҰӮеӣҫпјҡиҜ·д»”з»ҶзңӢеӣҫпјҢз”өжәҗйҖҡиҝҮиҝҮеӯ”иҝһжҺҘеҲ°100nFзҡ„з”өе®№з„ҠзӣҳдёҠпјҢ然еҗҺеңЁеҲ°10nFзҡ„з”өе®№пјҢжңҖеҗҺеҲ°з”өжәҗи„ҡгҖӮ

дҝқжҢҒPvddзҡ„зЁіе®ҡжҖ§е’ҢдҪҺеҷӘеЈ°жҳҜзү№еҲ«йҮҚиҰҒзҡ„пјҢдёҖе®ҡиҰҒжіЁж„Ҹз”өжәҗзҡ„зЁіеҺӢгҖҒж»ӨжіўгҖҒеҺ»и—•гҖӮејәзғҲжңҹжңӣжҜҸдёӘжЁЎжӢҹз”өи·Ҝ йғҪз”ұзӢ¬з«Ӣзҡ„з”өжәҗдҫӣз”өпјҡAvddгҖҒDvddгҖҒDvddioгҖҒPvddгҖӮ

жҹҗдәӣеӣҫеҪўжҺ§еҲ¶еҷЁеңЁжңүж•ҲпјҲеңЁжңүж•ҲеӣҫеғҸжңҹй—ҙпјүе’Ңз©әй—ІпјҲеҰӮиЎҢеҗҢжӯҘжІіеңәеҗҢжӯҘжңҹй—ҙпјүжңҹй—ҙзҡ„еҠҹиҖ—зә§еҲ«е·®ејӮеҫҲеӨ§пјҢиҝҷдјҡеҜјиҮҙжЁЎжӢҹз”өжәҗдҫӣз”өжіўеҠЁеҸҳеҢ–еҫҲеӨ§пјҢжүҖд»Ҙдҫӣз”өз”өжәҗйңҖиҰҒиҝӣиЎҢзЁіеҺӢж»ӨжіўеҺ»и—•гҖӮ

жҺЁиҚҗж•ҙдёӘPCBжқҝдҪҝз”ЁдёҖдёӘең°е№ійқўпјҢиҝҷдёӘең°е№ійқўзҡ„жЁЎжӢҹе’Ңж•°еӯ—йғЁеҲҶеә”иҜҘжңүдёӘз©әиўӯпјҢеҰӮдёӢеӣҫгҖӮ

ж— ж•°е®һи·өиЎЁжҳҺпјҢеҚ•дёҖзҡ„ең°е№ійқўзҡ„еҷӘеЈ°жҖ§иғҪеҸӘеҸҜиғҪдјҡжӣҙеҘҪпјҢдҪҝз”ЁеӨҡдёӘең°е№ійқўеҸҜиғҪжҳҜжңүе®ізҡ„пјҢеӣ дёәжҜҸдёӘеҲҶзҰ»зҡ„ең°е№ійқўжӣҙе°ҸпјҢй•ҝзҡ„ең°зҺҜзәҝеҸҜиғҪдјҡдә§з”ҹгҖӮ

еҪ“еҲҶзҰ»зҡ„ең°е№ійқўдёҚиғҪйҒҝе…Қзҡ„ж—¶еҖҷпјҢжҺЁиҚҗеңЁADV7180еә•дёӢж”ҫзҪ®дёҖдёӘең°е№ійқўпјҢеҲҶиЈӮзҡ„дҪҚзҪ®еә”иҜҘжҳҜеңЁADV7180еә•дёӢпјҢеңЁиҝҷз§Қжғ…еҶөдёӢпјҢжӯЈзЎ®ең°ж”ҫзҪ®е…ғ件жӣҙдёәйҮҚиҰҒпјҢеӣ дёәз”өжөҒзҺҜжӣҙеӨ§пјҢз”өжөҒжөҒз»Ҹзҡ„и·Ҝеҫ„зҡ„з”өйҳ»жңҖе°ҸгҖӮз”өжөҒзҺҜзҡ„дёҖдёӘдҫӢеӯҗжҳҜпјҡз”өжәҗе№ійқўеҲ°ADV1780пјҢ然еҗҺеҲ°ж•°еӯ—иҫ“еҮәзәҝпјҢеҶҚеҲ°ж•°еӯ—ж•°жҚ®жҺҘ收еҷЁйҒ“пјҢеҶҚеҲ°ж•°еӯ—ең°е№ійқўпјҢжңҖеҗҺеҲ°жЁЎжӢҹең°е№ійқўгҖӮ

PLL

PLLзҺҜи·Ҝзҡ„ж»Өжіўе…ғ件еә”иҜҘдёҺADV7180ж”ҫеңЁдёҖдёӘйқўдёҠпјҢд»ҘйҒҝе…ҚиҝҮеӯ”пјҢеҸҰеӨ–ж»ӨжіўеҷЁд»¶пјҢеә”иҜҘе°ҪеҸҜиғҪзҰ»з®Ўи„ҡиҝ‘пјҢеңЁж»ӨжіўеҷЁд»¶йҷ„иҝ‘дёҚиҰҒиө°ж•°еӯ—жҲ–й«ҳйў‘ж—¶й’ҹзәҝпјҢеҷЁд»¶зҡ„еҸӮж•°зІҫеәҰеә”иҜҘеңЁ10%жҲ–жӣҙдҪҺгҖӮ

VREFNе’ҢVREFP

ж»ӨжіўеҷЁд»¶еә”иҜҘдёҺADV7180ж”ҫеңЁдёҖдёӘйқўдёҠпјҢд»ҘйҒҝе…ҚиҝҮеӯ”пјҢеҸҰеӨ–ж»ӨжіўеҷЁд»¶пјҢеә”иҜҘе°ҪеҸҜиғҪзҰ»з®Ўи„ҡиҝ‘гҖӮеҗҰеҲҷдјҡдҪҝж•ҲжһңеӨ§жү“жҠҳжүЈгҖӮ

ж•°еӯ—иҫ“еҮәпјҲж•°жҚ®е’Ңж—¶й’ҹпјү

е°ҪйҮҸдҪҝиө°зәҝжңҖзҹӯпјҢзәҝи·Ҝи¶Ҡй•ҝпјҢеҲҶеёғзӯүж•Ҳз”өе®№и¶ҠеӨ§пјҢиҰҒжұӮи¶Ҡй«ҳзҡ„й©ұеҠЁз”өжөҒпјҢиҝҷж ·д№ҹдјҡеј•иө·жӣҙеӨҡзҡ„еҶ…йғЁж•°еӯ—еҷӘеЈ°пјҢиҖҢдё”зәҝзҹӯдәӣд№ҹдјҡеҮҸе°‘еҸҚе°„зҡ„еҸҜиғҪгҖӮ

дёІдёҖдёӘ30-50欧е§Ҷзҡ„еҸҜд»ҘжҠ‘еҲ¶еҸҚе°„пјҢеҮҸе°‘EMIпјҢеҮҸе°‘ADV7180еҶ…йғЁзҡ„зһ¬й—ҙжөӘж¶Ңз”өжөҒпјҢеҰӮжһңдҪҝз”ЁдёІиҒ”з”өйҳ»пјҢеә”иҜҘе°ҪеҸҜиғҪжҠҠе®ғ们ж”ҫеҲ°ADV7180з®Ўи„ҡйҷ„иҝ‘пјҢдҪҶиҝҷдёҚиҰҒд»ҘеўһеҠ иҝҮеӯ”жҲ–зәҝзҡ„й•ҝеәҰдёәд»Јд»·гҖӮ

е°ҪеҸҜиғҪеҮҸе°‘жҜҸдёӘж•°еӯ—иҫ“еҮәзҡ„й©ұеҠЁзҡ„з”өе®№пјҢдёҚиҰҒи¶…иҝҮ15pFпјҢиҝҷеҸҜд»ҘйҖҡиҝҮеҮҸе°‘зәҝзҡ„й•ҝеәҰд»ҘеҸҠд»…иҝһжҺҘдёҖдёӘеҷЁд»¶жқҘе®һзҺ°гҖӮеҮҸе°‘з”өе®№пјҢеҸҜд»ҘеҮҸе°‘ADV7180еҶ…йғЁзҡ„зһ¬й—ҙжөӘж¶Ңз”өжөҒпјҢд»ҺиҖҢеҮҸе°‘з”өжәҗдёҠзҡ„ж•°еӯ—еҷӘеЈ°гҖӮ

ADV7180еңЁеә•йғЁжңүдёӘйҮ‘еұһз„ҠзӣҳпјҢиҝҷдёӘз„Ҡзӣҳеҝ…йЎ»жҺҘең°пјҢиҝҷж ·дјҡеёҰжқҘдёӨдёӘеҘҪеӨ„пјҡеҲ©дәҺж•ЈзғӯпјҢеҮҸе°‘еҷӘеЈ°пјҢеўһеҠ жңәжў°ејәеәҰгҖӮ

ж•°еӯ—иҫ“е…Ҙ

ADV7180д»…ж”ҜжҢҒ3.3VдҝЎеҸ·пјҢ并дёҚиғҪжҺҘеҸ—5VдҝЎеҸ·пјҢжүҖд»ҘеҰӮжһңжңү5Vзҡ„йҖ»иҫ‘з”өе№іпјҢеә”иҜҘеўһеҠ з”өе№іиҪ¬жҚўеҷЁд»¶гҖӮ

еҲҶдә«еҲ°пјҡ

зӣёе…іжҺЁиҚҗ

йҖҡиҝҮFPGA硬件иҜӯиЁҖеҜ№зј–з ҒеҷЁADV7180иҝӣиЎҢIICй…ҚзҪ®пјҢеҸҜд»ҘзӣҙжҺҘ移жӨҚдҪҝз”Ё

adv7180 иҜҰз»Ҷж–ҮжЎЈпјҢ

freescale android adv7180 tvp5150 timeout

ADV7180зҡ„i2cй©ұеҠЁзЁӢеәҸпјҢVHDLиҜӯиЁҖејҖеҸ‘пјҢжңүиҜҰз»ҶжіЁйҮҠпјҢйҖӮеҗҲеҲқеӯҰиҖ…еӯҰд№ е’ҢеҸӮиҖғгҖӮ

adv7180 linux driver

ADV7180 DECODE иҠҜзүҮжүӢеҶҢ

ADIе…¬еҸёADV7180и§Ҷйў‘DecodeиҠҜзүҮзҡ„Linuxй©ұеҠЁгҖӮ

this files describe how to configure an ADV7180a

еңЁжҲ‘们еӯҰж ЎжЈҖзҙўж•°жҚ®еә“дёӯдёӢиҪҪзҡ„е…ідәҺADV7180зӣёе…іи®әж–ҮпјҢеҜ№дәҺејҖеҸ‘ADV7180зҡ„ејҖеҸ‘дәәе‘ҳпјҢеё®еҠ©дјҡзү№еҲ«еӨ§гҖӮ

з»ҸиҝҮйӘҢиҜҒзҡ„adv7180зҡ„й©ұеҠЁпјҢеёҢжңӣеӨ§е®¶еӨҡеӨҡеҲҶдә«пјҢеҸӘиҰҒеҲҶдә«е°ұиҮӘ然дјҡжңүз§ҜеҲҶдёӢиҪҪ

adv7180з”ЁдәҺжЁЎжӢҹж‘„еғҸеӨҙзҡ„и§Ҷйў‘и§Јз ҒпјҢдҪҝз”ЁиҜҘй©ұеҠЁдҪ еҸҜд»Ҙж–№дҫҝејҖеҸ‘еұһдәҺиҮӘе·ұзҡ„ж‘„еғҸеӨҙеә”з”ЁзЁӢеәҸгҖӮ

ADV7611еҸӮиҖғеҺҹзҗҶеӣҫдёҺPCB

adv7180 datasheet 10-Bit, 4Г— Oversampling SDTV Video Decoder

adv7180 иҠҜзүҮжүӢеҶҢпјҢADV7180иғҪеӨҹиҮӘеҠЁжЈҖжөӢдёҺе…ЁзҗғNTSCгҖҒPALе’ҢSECAMж ҮеҮҶе…је®№зҡ„ж ҮеҮҶжЁЎжӢҹеҹәеёҰз”өи§ҶдҝЎеҸ·,并е°Ҷе…¶иҪ¬жҚўдёәдёҺ8дҪҚITU-R.656жҺҘеҸЈж ҮеҮҶе…је®№зҡ„4:2:2еҲҶйҮҸи§Ҷйў‘ж•°жҚ®

AD7180й©ұеҠЁпјҢе®Ңж•ҙз ҒпјҢCеҸҜд»Ҙе…је®№д»»дҪ•е№іеҸ°гҖӮ

ADV7180иғҪеӨҹиҮӘеҠЁжЈҖжөӢдёҺе…ЁзҗғNTSCгҖҒPALе’ҢSECAMж ҮеҮҶе…је®№зҡ„ж ҮеҮҶжЁЎжӢҹеҹәеёҰз”өи§ҶдҝЎеҸ·,并е°Ҷе…¶иҪ¬жҚўдёәдёҺ8дҪҚITU-R.656жҺҘеҸЈж ҮеҮҶе…је®№зҡ„4:2:2еҲҶйҮҸи§Ҷйў‘ж•°жҚ®.

This code uses for fpga and ADV7180 interface.

ECP3 FPGA LFE3-17EA-328+ADV7611+CYUSB3014ејҖеҸ‘жқҝADи®ҫ计硬件еҺҹзҗҶеӣҫ+PCB(8еұӮ)е·ҘзЁӢж–Ү件пјҢ硬件йҮҮз”Ё8еұӮжқҝи®ҫи®ЎпјҢеӨ§е°Ҹдёә100*70mmпјҢеҢ…жӢ¬ALTIUMи®ҫи®Ўзҡ„е®Ңж•ҙеҺҹзҗҶеӣҫPCBж–Ү件пјҢеҸҜеҒҡдёәдҪ зҡ„еӯҰд№ и®ҫи®ЎеҸӮиҖғгҖӮ дё»иҰҒеҷЁд»¶пјҡ LFE3-17EA-...

fpga tvиҪ¬vga и§Јз ҒеҷЁadv7180пјҢи§Ҷйў‘иҪ¬жҚўadv7123

ADV7125ж•°еӯ— VGAжқҝALTIUMеҺҹзҗҶеӣҫ+PCB+е°ҒиЈ…еә“+BOMж–Ү件пјҢйҮҮз”Ё2еұӮжқҝи®ҫи®ЎпјҢжқҝеӯҗеӨ§е°Ҹдёә100x72mmпјҢеҚ•йқўеёғеұҖеҸҢйқўеёғзәҝпјҢдё»иҰҒеҷЁд»¶еҢ…жӢ¬ADV7125WBSTZ170пјҢEL4543IUпјҢPRTR5V0U2XзӯүеҷЁд»¶пјҢе®Ңж•ҙзҡ„BOMи®ҫи®Ўж–Ү件гҖӮAltiumDesigner и®ҫи®Ўзҡ„...